Available online at http://www.mecs-press.net/ijem

# Comparative Analysis of Various SRAM Cells with Low Power, High Read Stability and Low Area

Abhishek Agal<sup>a,\*</sup>, Pardeep<sup>b</sup>, Bal Krishan<sup>c</sup>

<sup>a</sup>M.Tech.(VLSI),G-41 Rajput colony, Subhash nagar, Bhilwara-311001, India <sup>b</sup> M.Tech.(VLSI),W.N. 15, Shiv colony, Safidon-126112, Jind, India <sup>c</sup>M.Tech.(Nanotechnology), Electronics Engineering Department. YMCA UST, Faridabad-121006, India

## Abstract

SRAMs are very important part of today's movable devices like laptops and mobile phones. Different SRAM cells of different number of transistors have their own respective advantages and drawbacks. In this work an attempt has been made to reduce the leakage power by adding some transistors. Each SRAM cell provides an efficient way to reduce the leakage power, but disadvantage of each SRAM cell limit the application of them.

In this paper, the study and transient analysis on four different SRAM cells has been carried out and compared with respect to various parameters like power dissipation, delay and area. The simulation is carried out in 180nm CMOS technology using tanner tools. Layout is carried out using microwind.

Index Terms: Delay, SRAM cell, SNM, Power Dissipation.

© 2014 Published by MECS Publisher. Selection and/or peer review under responsibility of the Research Association of Modern Education and Computer Science.

# 1. Introduction

The main objective of this work is evaluating performance in terms of power consumption, delay and area of various four SRAM cells in 180nm technology and comparing them with basic 6t SRAM cell.

Literature review and study of various SRAM cells is done. Transient analysis of all the SRAM cells is done and output is shown. The layouts are also shown. Result (power, delay and area) of all the SRAM cells has been shown and discussed. The project is developed in tanner tool v14.1. Microwind 3.1 is used for generating layout and calculating area.

Low leakage 10T SRAM cell has separated read port and stacked effect by M10 transistor, so it has BL leakage reduction feature [2].

High read stability 9T SRAM cell has separated read port so it has features of Read stability enhancement, 22.9% leakage power reduction and double read SNM as compare to 6T SRAM cell [3].

\* Corresponding author. Tel.: 9782692422, 8285950338

E-mail address: agal.abhishek@gmail.com

Low write power 7T SRAM cell has 49% write power saving but it is 17.5% larger than 6T SRAM cell due to one extra transistor [4].

Single ended 5T SRAM cell has 75% BL leakage reduction, 50% lower SNM and 23% smaller area as compared to 6T SRAM cell [5].

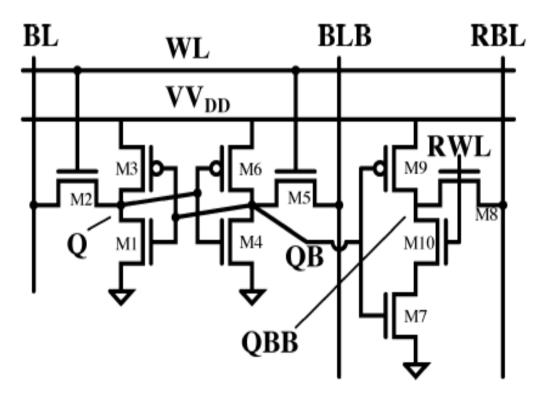

#### 1.1. Subthreshold 10T SRAM cell

As shown in the figure 1, it has separated read port i.e. separate BL and WL for read operation. Also it has stacked effect by M10 with M7 so the BL leakage is reduced.

To deeply understand the write operation, let us assume that WL signal is ON. So the pass transistor M2 and M5 connects the SRAM with signals BL and BLB. Now let us assume that, we have to write '1' at Q. So indirectly we are writing '0' at QB. For writing '1' at Q, we have to give '1' at BL and '0' at BLB. As the transistor M2 is ON because WL is high, so the data at BL directly forces Q to high and this is turn M4 ON and M6 OFF. So QB is discharged through M4 and becomes low, which alternately forces Q to high. So, finally we have logic 1 at Q.

To perform Read operation, we have to give logic '1' at WL so transistors M2 and M5 are turned on and also we have to give logic '1' at BL and BLB to read the value of Q at BL. The circuit with extra four transistors and two extra inputs RBL and RWL is used to reduce the leakage current of the SRAM cell. When we are performing read operation, we have to give logic '1' at RBL and RWL so transistors M8 and M10 are turned on and QB is inverted and output is stored at QBB, which is connected to RBL so we get the output at RBL.

Fig.1. Sub threshold 10T SRAM cell

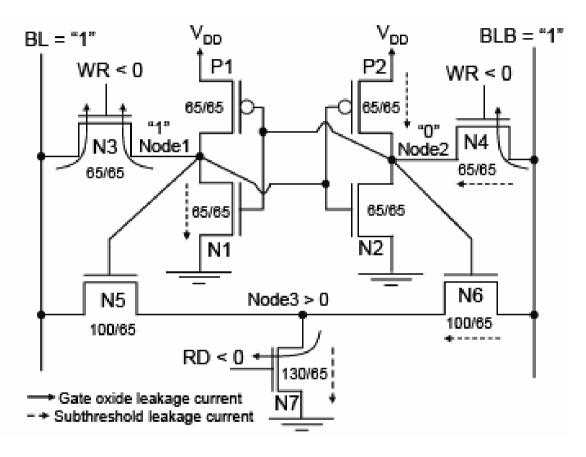

#### 1.2. High read stability and low leakage 9T SRAM cell

As shown in the figure 2, it has three extra transistors and one extra input RD as compare to basic 6T SRAM cell. It has separated read port.

During write operation WR goes "high" and RD goes "low", so transistor N7 is cut off and transistors N3 and N4 are turned on. As we pull WR to 1, transistors N3 and N4 are turned on and what we give at BL is written to Q.

During read operation RD goes "high" and WR goes "low", so transistor N7 turned on. To read, we apply logic 1 at BL and BLB. If Q has Logic 1 then it turns ON transistor N5, so BL signal is discharged through N5 and N7 i.e. the value at Q is stored at BLB.

Fig.2. High read stability and low leakage 9T SRAM cell

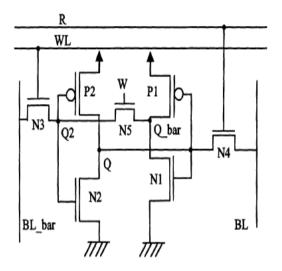

#### 1.3. Low write power 7T SRAM cell

As shown in figure, it has one extra transistor N5 and one extra input W as compare to basic 6T SRAM cell. The write operation starts by turning N5 off to cut off the feedback connection by giving logic 0 at W. N3 is turned on by applying logic 1 at WL. N4 is kept off so BL is disconnected to the circuit. So finally the value given to BLB is directly saved at QB and inverted data of QB is stored at Q. During read operation, it behaves like a conventional 6T SRAM cell i.e. N5 is kept on, which make it same as conventional 6T SRAM cell. When logic 1 is given to BL and BLB, the data at Q and QB charges or discharges BL and BLB accordingly. During all the process WL and R are given logic 1 so transistors N3 and N4 are turned ON to enable the read operation.

Fig.3. Low write power 7T SRAM cell

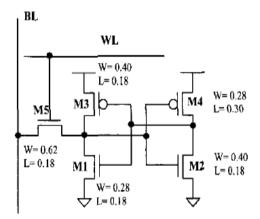

1.4. Single ended, low leakage 5T SRAM cell

As show in figure, it has single BL and single WL.

During read operation, BL is precharged to 600mV and then WL goes "high", so the data at Q stored at BL. During write operation, the data at BL is stored in Q as WL turns transistor M5 on.

Fig.4. Single ended, low leakage 5T SRAM cell

#### 2. Results and Waveforms

2.1. Subthreshold 10T SRAM cell

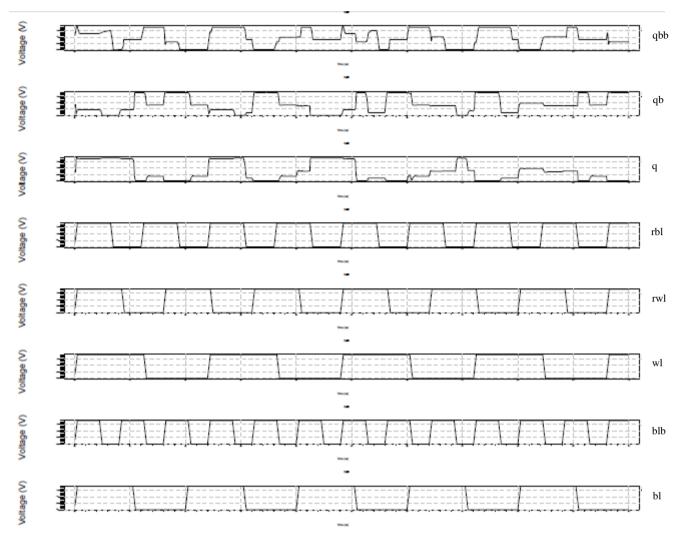

Fig.5. Output Waveform of Subthreshold 10T SRAM cell.

The subthreshold 10T SRAM cell has five inputs RBL, RWL, WL, BLB, BL and three outputs Q, QB, QBB as shown in waveform above. When WL is at logic '1', read or write operation takes place. When BL and BLB both are at logic '1', read operation is done i.e. the data at Q is taken at BL. When BL and BLB are different then each other, write operation is done i.e. the value of BL is written to Q.

Average power consumption is 9.175496 e-005 watts.

Read delay is 1.0950e-007 sec.

Write delay is 8.0360e-008 sec.

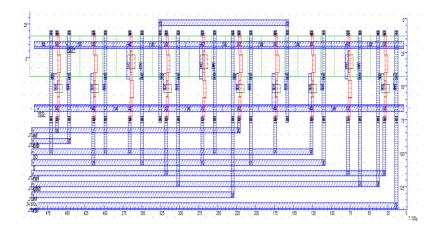

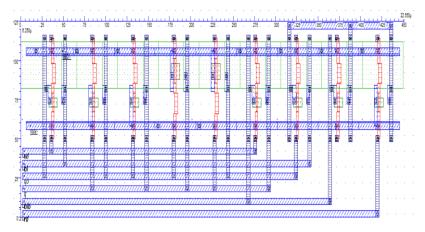

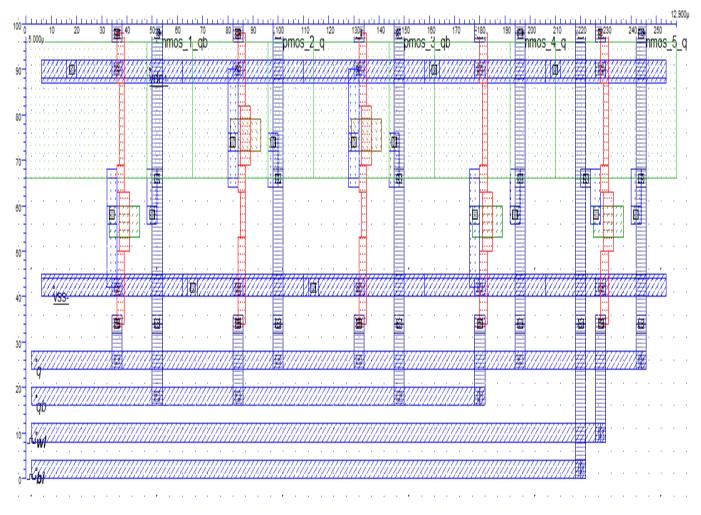

The layout shows that total area is 24.9\*7.1 (um) ?

Fig.6. Layout of Subthreshold 10T SRAM cell

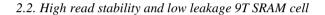

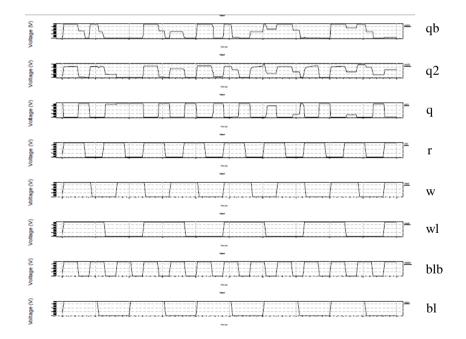

Fig.7. Output waveform of High read stability and low leakage 9T SRAM cell

The high read stability and low leakage 9T SRAM cell has four inputs BL, BLB, WR, RD and two inputs Q, QB as shown in the waveform above.

Average power consumption is 1.092888e-004 watts.

Read delay is 6.5000e-008 sec.

Write delay is 2.0482e-009 sec.

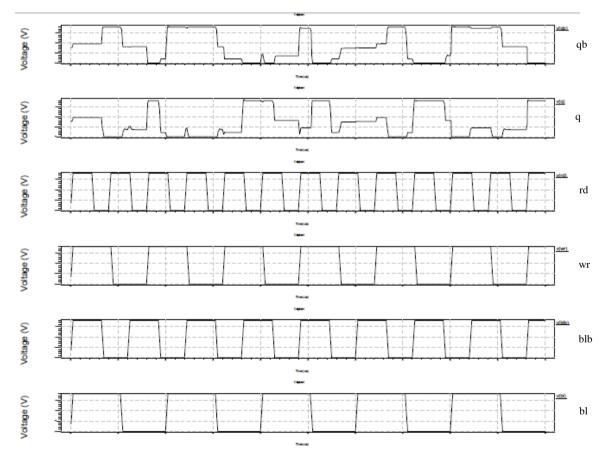

The layout shows that total area is 22.5\*6.2 (um) ?

Fig.8. Layout of High read stability and low leakage 9T SRAM cell

2.3. Low write power 7T SRAM cell

Fig.9. Output waveform of Low write power 7T SRAM cell

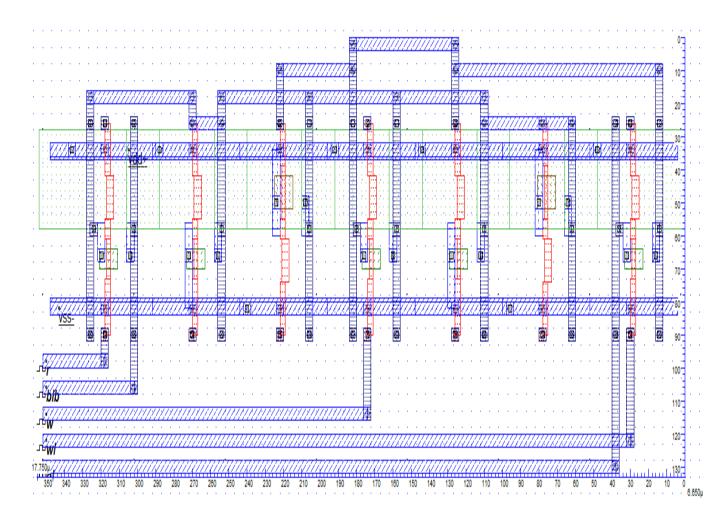

As shown in the waveform above, the low write power 7T SRAM cell has five inputs BL, BLB, WL, W, R and three outputs Q, Q2, QB which are measured and shown above.

Average power consumption is 2.358070e-005 watts.

Read delay is 1.275e-007 sec.

Write delay is 2.1e-007 sec.

The layout shows that total area is 17.7\*6.6 (um) ?

Fig.10. Layout of Low write power 7T SRAM cell

2.4. Single ended, low leakage 5T SRAM cell

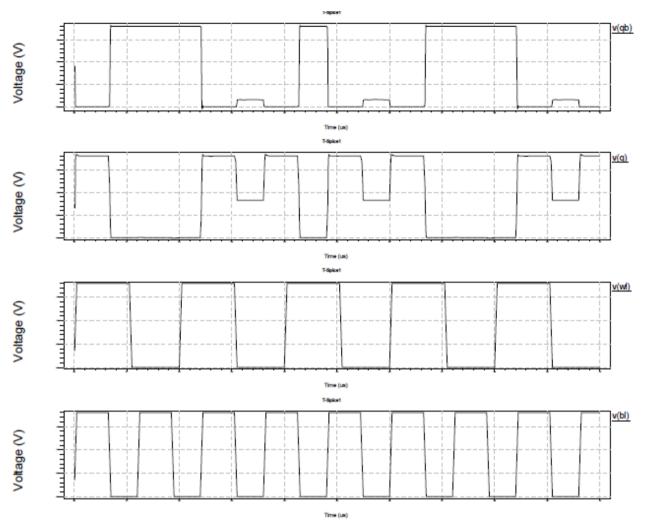

Fig.11. Output waveform Single ended, low leakage 5T SRAM cell

As shown above, this SRAM cell has two inputs BL, WL and two outputs Q, QB which are measured as above.

Average power consumption is 3.604690e-006 watts.

Read delay is 6.5000e-008 sec.

Write delay is 1.3064e-009 sec.

The layout shows that total area is 12.9\*5.0 (um) <sup>2</sup>.

Fig.12. Layout of Single ended, low leakage 5T SRAM cell

# 3. Conclusion

10

Comparison of these four SRAM cells is shown in the table bellow according to the parameters power consumption, read delay, write delay, area.

Table 1: comparison of various SRAM cells

| SRAM cell | POWER<br>CONSUMTION<br>(uW) | READ<br>DELAY<br>(n sec.) | WRITE<br>DELAY<br>(n sec.) | AREA<br>(um) <sup>2</sup> |

|-----------|-----------------------------|---------------------------|----------------------------|---------------------------|

| Basic 6T  | 131.7                       | 0.47                      | 0.96                       | 116.82                    |

| 5T        | 3.6                         | 65.0                      | 1.3                        | 64.5                      |

| 7T        | 23.6                        | 127.5                     | 210                        | 116.82                    |

| 9T        | 109.3                       | 65.0                      | 2.0                        | 139.5                     |

| 10T       | 91.7                        | 109.5                     | 80.4                       | 176.79                    |

In this paper comparison of various SRAM cells is done with respect to parameters like power dissipation, read delay, write delay and area as shown in the table above by using tanner tools software. In these SRAM cells, the read, write delays and area are increased but power dissipation is much reduced accordingly. Even 5T SRAM cell has low area consumption with respect to conventional 6T SRAM cell.

## Acknowledgements

For power constrained projects like space exploration and satellites the SRAM cell which consumes minimum power should be used while for very fast processing devices the SRAM cell which has minimum time delay should be used. The design of SRAM cell can be optimized by tradeoffs between various performance parameters.

#### References

- [1] Abhishek Agal, Pardeep, Bal Krishan. 6T SRAM cell: Design and Analysis. IJERA; Volume 4, Issue 3(Version 1); March 2014; pp 574-577.

- [2] B. Calhoun & A. Chandrakasan. A 256-kb 65-nm Sub-threshold SRAM Design for Ultra-Low-Voltage Operation. JSSC, 2007.

- [3] Z. Liu and V. Kursun. High Read Stability and Low Leakage Cache Memory Cell. IEEE Conference, 2007.

- [4] R. Aly, M. Faisal and A. Bayoumi. Novel 7T SRAM Cell For Low Power Cache Design. IEEE SoC Conf., 2005.

- [5] I. Carlson et.al. A High Density, Low Leakage, 5T SRAM for Embedded Caches. ESSCIRC, 2004.

- [6] Ajay Kumar Dadoria, Arjun Singh Yadav C.M Roy. Comparative Analysis of Variable N-T Sram Cells. International Journal of Advanced Research in Computer Science and Software Engineering; Volume 3, Issue 4; April 2013.

- [7] Sapna singh, Neha Arora, Meenkshi Suthar, Neha Gupta. Performance evaluation of different SRAM cell structures at different technologies. International Journal of VLSI design& communication systems (VLSICS); vol.3, No.1; February 2012.

- [8] Andrei Pavlov, Manoj Sachdev. CMOS SRAM Circuit Design and parametric test in nano-scaled technologies, Process Aware SRAM Design and Test. Springer; 2008.

- [9] N. Kim, K. Flautner, D. Blaauw, and T. Mudge. Circuit and microarchitectural techniques for reducing cache leakage power. IEEE Trans. Very Large Scale Integr. (VLSI) Syst.; vol. 12, no. 2; pp. 167–184; Feb. 2004.

- [10] K. Kanda, T. Miyazaki, M. K. Sik, H. Kawaguchi, and T. Sakurai. Two orders of magnitude leakage power reduction of low-voltage SRAM's by row-by-row dynamic V control (RRDV) scheme. in Proc. IEEE Int. ASIC/SOC Conf.; Sep. 2002; pp. 381–385.

- [11] A. Alvandpour, D. Somasekhar, R. Krishnamurthy, V. De, S. Borkar, and C. Svensson. Bitline leakage equalization for sub-100 nm caches. in Proc. ESSCIRC; 2003; pp. 401–404.

- [12] E. Grossar, M. Stucchi, K. Maex, W. Dehaene. Read Stability and Write-Ability Analysis of SRAM Cells for Nanometer Technologies. IEEE Journal of Solid-State Circuits; vol. 41; pp. 2577 – 2588; Nov. 2006.

- [13] Raychowdhury, S. Mukhopadhyay, K. Roy. A feasibility study of subthreshold SRAM across technology generations. Proc. of International Conference on Computer Design; pp. 417-422; October 2005.

- [14] N. Yoshinobu, H. Masahi, K. Takayuki, K. Itoh. Review and future prospects of low-voltage RAM circuits. IBM journal of research and development; vol. 47, No. 5/6; pp.525-552; 2003.

- [15] Sanjay Singh, Ravi Saini, Anil K. Saini, AS Mandal, Chandra Shekhar, Anil Vohra. Performance Evaluation of Different Memory Components for FPGA based Embedded System Design for Video

## 12 Comparative Analysis of Various SRAM Cells with Low Power, High Read Stability and Low Area

Processing Application. I.J. Intelligent Systems and Applications; MECS; Nov. 2013; 12; 113-119.

## Author(s) Profile

Abhishek Agal received his Master of Technology in VLSI Design from YMCA University of Science and Technology, Faridabad, Haryana, India and Bachelor of Technology in Electronics and Communication from Institute of Technology and Management, Bhilwara, Rajasthan, India. His research interests are SRAMs, VLSI architectures, HDLs, Embedded System Design, ASIC Design, VLSI Design and Design Methodologies. He has published several research papers in various reputed international/national journals.

**Pardeep** received his Master of Technology in VLSI Design from YMCA University of Science and Technology, Faridabad, Haryana, India and Bachelor of Technology in Electronics and Communication from N.C. College of Engineering, israna, panipat, haryana, India. His research interests are CMOS Comparators, Embedded system, VLSI Design, Robotics and IC fabrication. He has published several research papers in various reputed international/national journals.

**Bal krishan** received his B.E. degree in Electronics & Communication Engineering from CRSCE (Now Govt. University), Murthal (Sonepat), Haryana in 1997 and M.TECH. degree in Nanotechnology from JMI, Delhi in 2009 respectively. During 2007-2009, he stayed in Materials Science Laboratory, Jamia Millia Islamia, N.Delhi to study synthesis, characterization, I-V studies and field emission properties of carbon nanotube. He has supervised 10 M.Tech. and many B.Tech. projects. He has published many papers in various National & International conferences / journals.

He is pursuing Ph.D in the field of Nano electronics from YMCA UST, Faridabad (Haryana). Presently he is working as Assistant Professor in Electronics Engineering Department. YMCA UST, Faridabad.

Research Interests: Nano electronics & devices, VLSI Design, Electronics Engg.

How to cite this paper: Abhishek Agal, Pardeep, Bal Krishan, "Comparative Analysis of Various SRAM Cells with Low Power, High Read Stability and Low Area", IJEM, vol.4, no.3, pp.1-12, 2014.DOI: 10.5815/ijem.2014.03.01