Available online at http://www.mecs-press.net/ijwmt

# Design of Adder Using Quantum Cellular Automata

K.Sundara Rao<sup>1</sup>, Mrudula Singamsetti<sup>2</sup>, Vuyyuru Tejaswi<sup>3</sup>

Department of Electronics & Communication Engineering Vignan's Foundation for Science, Technology and Research, Guntur-522213, A.P, India

Received: 17 July 2019; Accepted: 09 August 2019; Published: 08 November 2019

## Abstract

QCA is the trending technologies for designing less hardware and low power consumed circuits measured in Nano-scale. These QCA cells are accustomed to construct combinational and sequential circuits. In this paper we presented a design for developing a basic arithmetic unit called full adder using Quantum cellular automata. The new submitted FA consists fewer amounts of quantum cells and delay also minimizes, when compared with the existing architecture.

Index Terms: Full adder (FA), Majority Gate (MG). QCA cell.

© 2019 Published by MECS Publisher. Selection and/or peer review under responsibility of the Research Association of Modern Education and Computer Science

## 1. Introduction

QCA were introduced by Lent C.S. and Tougaw. P.D [1]. This technology consumes very less area, low power dissipation, less leakage current. This technology made of six come up technologies regarding future computers. In [3], it explains logical expressions implemented by utilizing majority gates (MG) and inverters. In [2], it explains how to implement QCA circuits using majority gate and inverter gate. With these we can implement basic circuits, adders [4], mux [6,7], flip-flops [5], etc...

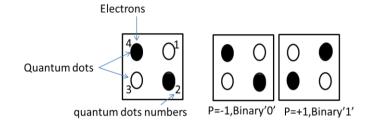

Adders are the fundamental element in the ALU's and Multiplications Units. The adder block is implemented by XOR, AND logic gates which performs binary arithmetic operations. Conniving a latest adder design utilizing QCA technology do a leading part in majority of the integrated circuit design. QCA consists of quantized cells, composed of 4 quantum dots located at the edges of the basic quantum cell shown in fig1. The electronic charge is confined in the polarized dots. The polarized electrons can tunnel in to the dots which are diagonal placed because of columbic repulsion. But they cannot tunnel in to the adjacent cells because of \* Corresponding author.

E-mail address: kagithasundar@gmail.com, mrudulasingamsetti@gmail.com

potential barrier exists in the middle of the adjacent dots.

Fig.1. Basic Quantum Cellular Automata Structure

The 2 quantum dots and 2 electrons arrangement of a basic QCA structure is represented in the fig1. The expression of the polarization(P) of the quantum cell is shown in eq.1 [8]. P=-1 is represented as binary logical value'0' and P=+1 is represented as binary logical value'1' [16, 17], as shown in the fig.1.

$$P = \frac{(P1+P3) - (P2+P4)}{P1+P2+P3+P4} \tag{1}$$

Here p1, p2, p3, p4 designates the electrons that are located in the QCA basic structure. All the digital circuit designs are formulated utilizing QCA

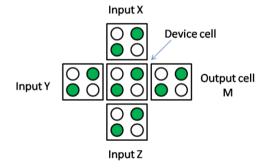

QCA circuits are formulated utilizing majority gate which comprise of 5 QCA cells, out of which 3 are inputs,1 output and 1 processing cell shown in the fig.2.

Fig.2. Majority Gate of 5 cells QCA

The logical expression of an MG is given in the eq.2.

$$f(a,b,c) = a.b + b.c + c.a \tag{2}$$

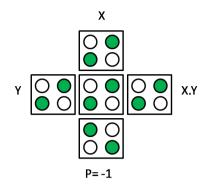

Designing digital circuits can be done by utilizing majority gates. From eq.2 one of the input is zero i.e assume c='0', then the majority gate works as a logical AND gate shown in fig.3.

$$f(a,b,0) = a.b \tag{3}$$

Fig.3 QCA design for an AND Gate

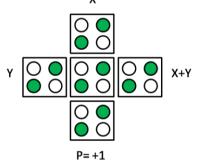

From eq.2 if c='1', then the MG works as a logical OR gate shown in fig.4

$$f(a,b,1) = a+b \tag{4}$$

Fig.4 QCA design for an OR Gate

The QCA design for an inverter which is shown in fig.5

Fig.5 QCA design for an inverter

# 2. Literature Survey for the adder Design using QCA

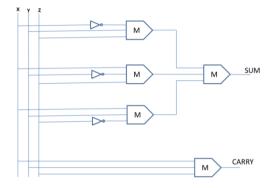

A full adder is a design which adds 3 binary inputs and obtain 2 outputs Sum and Carry. The formulae for sum and carry using majority gates is given in eq.5 and eq.6. Finally, full adder structure requires five majority gates and three basic inverters [9] which is shown in fig.6.

$$Carry = f(a, b, c) \tag{5}$$

$$Sum = f(f(a, b, c), f(a, b, c), f(a, b, c))$$

(6)

Fig.6 Basic Full adder using Majority gates

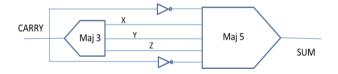

K. Navi [10] has proposed different logical expression which is given in the eq.7 ,eq.8 and its logical diagram is shown in fig.7.

$$Carry = f(a, b, c) \tag{7}$$

$$Sum = f(carry, carry, a, b, c)$$

(8)

Fig.7. [10] Full adder QCA design

From [10] adders is developed by utilizing 3 input XOR gate [18] and five input majority gate. The 3 input XOR based on QCA is shown in fig.8 comprising 14 cells and assign one of the input is zero which behaves as an XOR gate.

Fig.8. [18] 3-input XOR gate QCA design

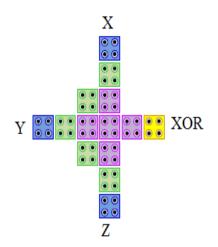

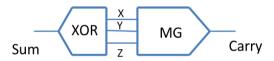

# 3. Proposed design for Full adder using QCA

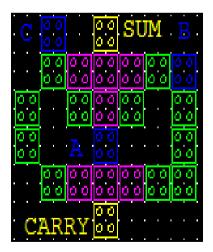

The structural design of the proposed design which comprising of 3 input majority gate and an XOR gate is shown in fig.9. The proposed design has 23 standard cell structure by using 2 clocks is shown in fig.10. Blue color represents full adder inputs, yellow color designated outputs and the remaining colors related to setup, hold, relax and release phases

Fig.9 Proposed Full adder using 3 input XOR gate and majority gate

Fig.10. Proposed Full adder design using QCA

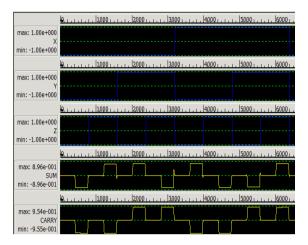

#### 4. Simulated Results for the proposed adder

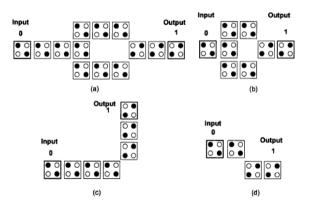

The possible output and input combinations are shown in fig.11.

Fig.11. Simulated results of the waveform of proposed FA.

Table I shows the comparative analysis of full adder design using QCA. From Ref [8] the full adder has been constructed using 38 standard cell structure in which delay is more [11]. The proposed design requires the 23 standard QCA cell structure has better performance in terms of area and delay.

Table1. Comparative Analysis of QCA based Full adder design

| Circuit       | No.of QCA<br>cells | Area in Nano<br>square meters | No.of Clock<br>Phases |

|---------------|--------------------|-------------------------------|-----------------------|

| In Ref. [9]   | 192                | 190244                        | 4                     |

| In Ref. [12]  | 145                | 179901                        | 4                     |

| In Ref. [13]  | 107                | 115781                        | 4                     |

| In Ref. [14]  | 61                 | 40512                         | 3                     |

| In Ref. [15]  | 51                 | 37054                         | 3                     |

| In Ref. [8]   | 38                 | 30568                         | 3                     |

| In Ref. [11]  | 31                 | 23598                         | 2                     |

| New Structure | 23                 | 16284                         | 2                     |

#### 5. Conclusions

The new structure for QCA based full adder which occupies less area in terms of QCA cell structures, number of clock phases, Area in Nano square meters compared to the other full adder architectures mentioned in the literature. The limitation for the proposed design is unable to reduce the number of clock because data transfer will not takes place.

#### References

- [1] Lent.C, Tougaw.P, "A device architecture for computing with quantum dots", Proceedings of the IEEE, vol. 85, pp. 541-557, 1997.

- [2] Farazkish.R, Azghadi.M, Haghparast.M and Navi.K,"New Method for Decreasing the Number of Quantum-dot Cells in QCA Circuits," World Applied Sciences Journal, vol. 6, pp. 793-802, 2008.

- [3] Oya.T, Asai.T, Fukui.T, and Amemiya.Y, "A Majority-Logic Device Using an Irreversible Single-Electron Box," IEEE Transactions on Nanotechnology, vol. 2, 2003.

- [4] Navi.K, Farazkish.R, Sayedsalehi.S, and Azghadi.M.R, "A New Quantum-dot Cellular Automata Fulladder," Microelectronics Journal, vol. 41, p. 820826, 2010.

- [5] Dutta.P ,Mukhopadhyay.D, "New Architecture for Flip Flops using Quantum-dot Cellular Automata," Proceedings of the 48th Annual Convention of Computer Society of India Vol II Advances in Intelligent Systems and Computing, Springer-Verlag, vol. 249, pp. 707-714, 2013.

- [6] Mukhopadhyay.D,Dutta.P,Dinda.S, Designing and Implementation of Quantum Cellular automata 2:1 Multiplexer Circuit," International Journal of Computer Applications, vol. 25, no. 1, pp. 21- 24, 2011.

- [7] Mukhopadhyay.D,Dutta.P, " Quantum Cellular Automata Based Novel Unit 2: I Multiplexer," International Journal of Computer Applications, vol. 3, pp. 22-25, 2012.

- [8] Mohammadi.M, S. Gorgin, M. Mohammadi, "An efficient design of full adder in quantum technology", Microelectronics Journal, No.50, pp. 35-43, 2016.

- [9] Douglas.Tougaw.P, Lent.C.S, "Logical devices implemented using quantum cell Mar automata" Department of Electrical Engineering, Universi~ of Notre Dame, Notre Dame, Indiana 46556 (Received 28 July 1993; accepted for publication 26 October 1993)

- [10] Navi.K, Sayedsalehi.S, Farazkish.R, Azghadi.M.R,"A new quantum dot cellular automata full adder", Microelectronics Journal, no. 41, pp. 820-826, 2010.

- [11] NuriddinSafoev and Jun-CheolJeon "Full Adder Based on Quantum-dot Cellular Automata" 2017 Manila International Conference on "Trends in Engineering and Technology" (MTET-17) Jan. 23-24, 2017 Manila (Philippines).

- [12] Devi.T.R, "Implementation of adder by using QCA technology", 1993

- [13] Peer Zahoor Ahmad, Dr. Rafiq Ahmad Khan , Firdous Ahmad, B. Syed Muzaffar Ahmad, "Implementation of Quantum dot Cellular Automata based Novel Full Adder and Full Subtractor" International Journal of Science and Research (IJSR)Volume 3 Issue 8, August 2014.

- [14] Navi.K, S. Saedsalehi, Farazkish.R, Azghadi.M.R, "Five-input majority gate, a new device for quantum dot cellular automata", J. Comput. Theor. Nanosci, vol. 7, pp. 1546-1553, 2010.

- [15] Hashemi.S, Tehrani.M, Navi.K, "An efficient quantum-dot cellular automata full-adder", Sci. Res. Esseys, vol. 7, no. 2, pp. 177-189, 2012.

- [16] Snider.O, Amlani.I, Bernstein, Lent.C.S, Merz.J.L, Porod.W, "A functional cell for quantum dot cellular automata, Solid-State Electron", vol. 42, pp. 1355-1359, 1998.

- [17] Jeon.J.C, "Low hardware complexity QCA decoding architecture using inverter chain", International Journal of Control and Automation, vol. 9, no. 4, pp. 347-358, 2016.

- [18] Ahmad.F, Bhat.G.M, Khademolhosseini.H, Azimi.S, Angizi.S,Navi.K, "Towards single layer quantum dot cellular automata adders based on explicit interaction of cells", Journal of Computer Science, vol. 16, pp.8-15, 2016.

# **Authors' Profiles**

**K.Sundara Rao** was born in Rajamahendravaram, Andhrapradesh, India. He completed his graduation (B.Tech), ECE in VFSTR ,Vadlamudi (2015) and completed his (M.Tech), ECE under the specialization in VLSI Design fromVFSTR,Vadlamudi (2018). He is doing research on Quantum-dot Cellular Automata.

**Ms. Singamsetti Mrudula** completed her graduation in B. E in the department of ECE, REC, sriperumbudur, Chennai, India, (2007) and completed her masters in Engineering domain in VLSI System Design in VNRVJIET, Telangana, India, 2009.She is currently working as an Asst. Professor in the Department of ECE, VFSTR. Her research area includes Quantum-dot Cellular Automata, Floating point Multipliers, VLSI testing and verification.

**Ms.Tejaswi** completed her post-graduation in Vignan's Foundation for science technology and research in the department of ECE .She is currently working as an assistant professor in the department of ECE,VFSTR. Her research area includes Quantum cellular Automata,Image processing

**How to cite this paper:** K.Sundara Rao, Mrudula Singamsetti, Vuyyuru Tejaswi, "Design of Adder Using Quantum Cellular Automata", International Journal of Wireless and Microwave Technologies(IJWMT), Vol.9, No.6, pp. 11-18, 2019.DOI: 10.5815/ijwmt.2019.06.02